# AstroByte:

# Programmable and Scalable Multi-FPGA Interconnect infrastructure for Accelerated Simulations of Self-Repairing Spiking Astrocyte Neural Networks

Shvan Haji Karim

Faculty of Computing, Engineering and the Built Environment

A thesis submitted for the degree of Doctor of Philosophy (PhD)

April 2020

"I confirm that the word count of this thesis is less than 100,000 word"

# Before fire-worshiping, before being Muslims, Whether being captives or free, We have always been *Kurds* and we will forever remain so

Ibrahim Ahmad

## Table of contents

| Table of cor   | ntents                                                       | 3  |

|----------------|--------------------------------------------------------------|----|

| Acknowledg     | gement                                                       | 6  |

| ABSTRACT       |                                                              |    |

| ist of Figures |                                                              |    |

| List of Table  | es                                                           | 9  |

| List of acror  | nyms and abbreviations                                       | 9  |

| Chapter 1: I   | ntroduction                                                  | 13 |

| 1.1 B          | ackground                                                    | 13 |

| 1.2 N          | lotivation                                                   | 14 |

| 1.3 T          | hesis Hypothesis and Contributions                           | 16 |

| 1.4 T          | hesis Outline                                                | 17 |

| 1.5 P          | Publications                                                 | 18 |

| Chapter 2: L   | _iterature Review                                            | 20 |

| 2.1 N          | leuron Models                                                | 20 |

| 2.1.1          | Hodgkin-Huxley (HH) Model                                    | 20 |

| 2.1.2          | Pinsky-Rinzel Model                                          | 21 |

| 2.1.3          | FitzHugh-Nagumo Model                                        | 21 |

| 2.1.4          | Leaky Integrate and Fire Neurons                             | 22 |

| 2.2 A          | strocyte and Tripartite Synapse                              | 23 |

| 2.2.1          | Astrocyte Models                                             | 23 |

| 2.2.2          | An Astrocyte Model for Self-repairing Hardware               |    |

| 2.2.3          | Astrocyte Hardware Implementations                           | 30 |

| 2.2.4          | Hardware Interconnection Paradigms for Astrocytic Signalling | 32 |

| 2.3 S          | NN FPGA Implementations                                      | 34 |

| 2.4 S          | piNNaker                                                     | 39 |

| 2.5 F          | PGA Data Acquisition Platforms                               | 39 |

| 2.6 N          | loC Background                                               | 40 |

| 2.6.1          | NoC Terminology                                              | 40 |

| 2.6.2          | Networks-on-Chip Topologies                                  | 40 |

| 2.6.3          | Networks-on-Chip Flow Controls                               | 41 |

| 2.6.4          | Routing Algorithms                                           | 43 |

| 2.7 N          | fain Challenges                                              | 43 |

| 2.7.1          | Incorporating Astrocytes in SNNs                             | 43 |

| 2.7.2          | Astrocyte Process Optimization                               | 43 |

|     | 2.7.3          | Networks-on-Chip Interconnection Paradigm for SANNs                           | 43 |

|-----|----------------|-------------------------------------------------------------------------------|----|

|     | 2.7.4<br>Hardw | Methodology for Configuration and Monitoring of FPGA-bavare Accelerators      |    |

| 2   | 8              | Chapter Conclusion                                                            | 44 |

| Cha | apter 3:       | A Biologically Faithful SANN Model for FPGAs                                  | 45 |

| 3   | s.1 <i>A</i>   | AstroByte Platform Overview                                                   | 45 |

| 3   | s.2 A          | Astrocyte Hardware Architecture                                               | 46 |

| 3   | 3.3 F          | SA Evaluation and Hardware Implementation                                     | 49 |

|     | 3.3.1          | Fault modelling in SANNs                                                      | 50 |

|     | 3.3.2          | Self-repair - Reduced Bit Precision                                           | 52 |

|     | 3.3.3          | Self-repair over Varied Fault Rates                                           | 53 |

|     | 3.3.4          | FSA Acceleration Performance                                                  | 55 |

| _   |                | FPGA-based Configuration and Monitoring Platform for Self-<br>g SANN Hardware | 56 |

|     | 3.4.1          | Architecture and Operation                                                    | 57 |

|     | 3.4.2          | Experimentations and Results                                                  | 60 |

| 3   | 5.5            | Chapter Conclusion                                                            | 66 |

| Cha | apter 4:       | A Networks-on-Chip based Multi-FPGA Infrastructure                            | 67 |

| 4   | .1 /           | AstroByte Platform Overview                                                   | 67 |

| 4   | .2 <i>F</i>    | AstroByte frequencies                                                         | 69 |

| 4   | .3 I           | ntel GXB transceiver IP                                                       | 69 |

| 4   | .4             | AstroByte NoC Data Format                                                     | 69 |

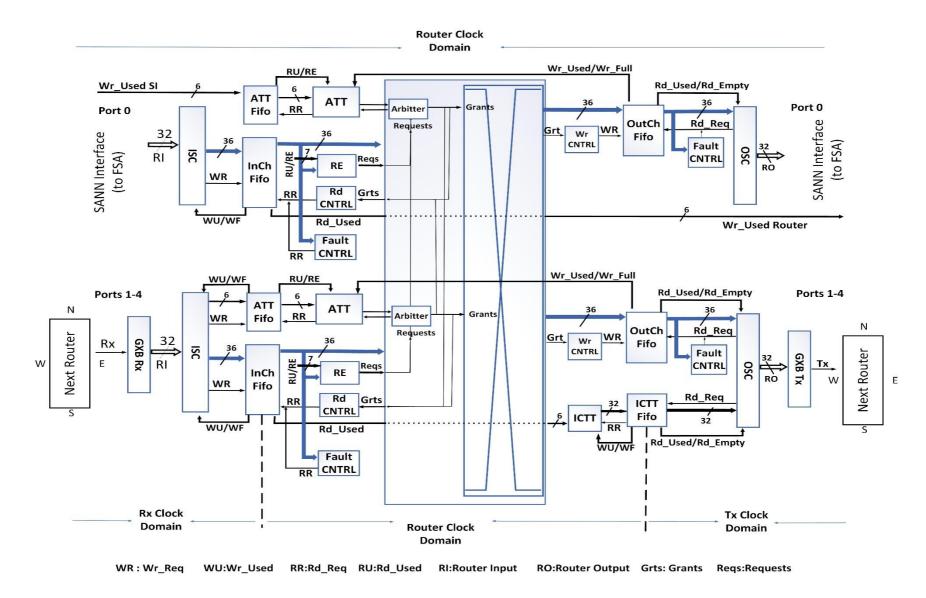

| 4   | .5 A           | AstroByte Router Architecture                                                 | 71 |

| 4   | .6 F           | Router Design and Operation                                                   | 81 |

| 4   | .7 F           | FSA & FCMP Interfaces                                                         | 82 |

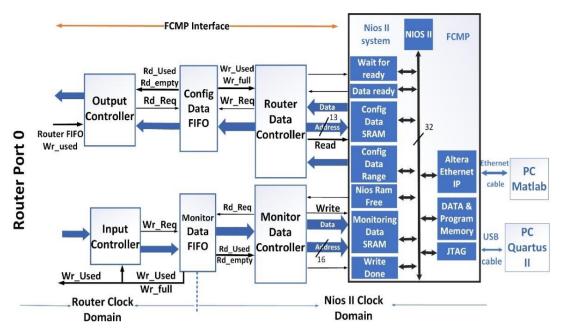

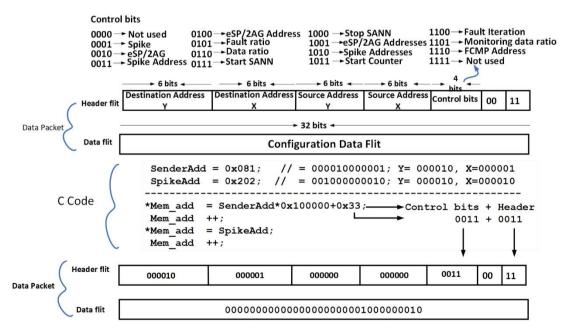

|     | 4.7.1          | FCMP                                                                          | 83 |

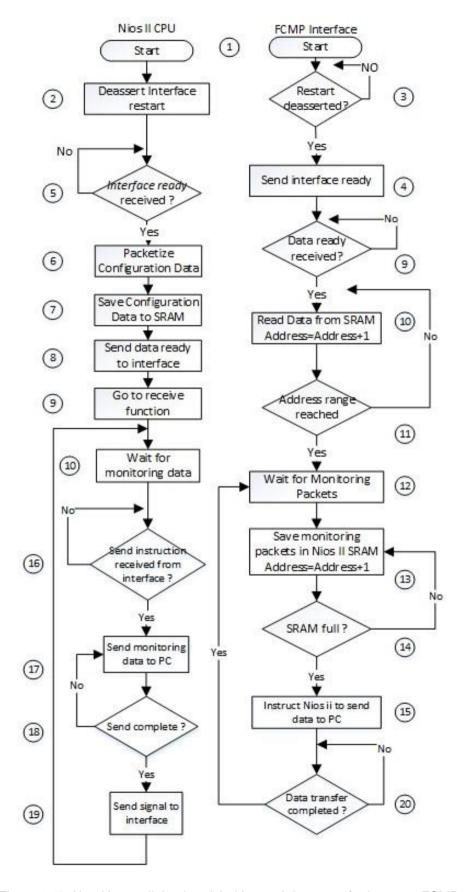

|     | 4.7.2          | FCMP Interface (FI)                                                           | 84 |

|     | 4.7.3          | Router Data Controller (RDC)                                                  | 85 |

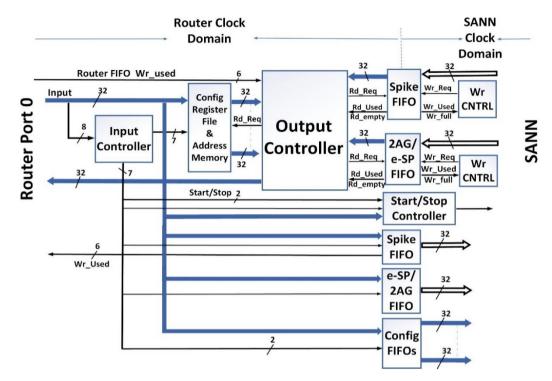

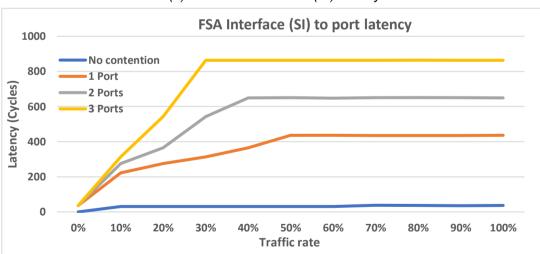

|     | 4.7.4          | FSA Interface (SI)                                                            | 85 |

| 4   | .8             | Chapter conclusion                                                            | 91 |

| Cha | apter 5:       | Experimentation and Results                                                   | 92 |

| 5   | 5.1 E          | Experiment setup                                                              | 92 |

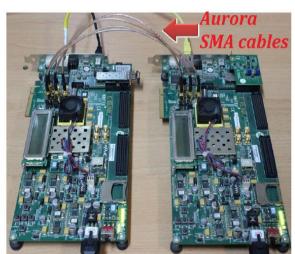

| 5   | 5.2 N          | Multi-FPGA Setup                                                              | 92 |

| 5   | 5.3            | Throughput calculations                                                       | 95 |

| 5   | 5.4 L          | _atencv                                                                       | 99 |

| 5.5                                    | Simulations and Under-sampling       | 101 |

|----------------------------------------|--------------------------------------|-----|

| 5.6                                    | Multi-FPGA SANN implementation       | 102 |

| 5.7                                    | SANN multi-FPGA simulation           | 103 |

| 5.7.1                                  | 1 Acceleration                       | 104 |

| 5.7.2                                  | 2 Accuracy                           | 105 |

| 5.7.3                                  | 3 Comparison with SNAVA and Bluehive | 109 |

| 5.8                                    | Chapter conclusion                   | 110 |

| Chapter 6: Conclusion and future work1 |                                      | 112 |

| 6.1                                    | Concluding summary                   | 112 |

| 6.2                                    | Main contributions                   | 112 |

| 6.3                                    | Future work                          | 113 |

| 6.4                                    | Self-critic                          | 115 |

| Reference                              | es                                   | 116 |

| Appendix                               |                                      | 127 |

| Intel tra                              | ansceiver operation and architecture | 127 |

| Dual C                                 | lock FIFO (DCFIFO) memories          | 135 |

| Cont                                   | trollers for DCFIFOs                 | 137 |

# Acknowledgement

I would like to genuinely thank Ulster University and the EPSRC funding council grants (EP/N00714X/1 & EP/N007050/1) for providing me with this opportunity to study a PhD degree through the Vice Chancellor's Research Scholarship (VCRS).

My special thanks go to my PhD supervisors, Dr Jim Harkin, Prof. Liam McDaid and Dr Bryan Gardener, for their advice and guidance during the period of this doctoral research.

I also thank Dr John Wade for his help with the original astrocyte model code and his guidance at the start of the PhD program. Likewise, I thank the other participants of the SPANNER project. Dr Junxiu Lui (Ulster University), Dr Andrew Tyrrell, Dr David Halliday, Dr Jon Timmis, Dr Anju Johnson and Dr Allan Millard (University of York).

Similarly, I thank all the staff at ISRC, Ulster University Doctoral College, Ulster University Research Office and throughout Ulster University generally. Their efforts helped the PhD program proceed smoothly.

My deepest gratitude goes to my family, my mother Dlxwaz, my sisters Shaee and Shang, and my father Ali, whose soul will always be with us. It was because of him I learnt dedication in life, love for science and love for humanity.

Finally, I truly thank the President of Komar University Dr Salahalddin Saeed Ali, the head of Ulster University Doctoral College Professor Alison Gallagher, Senior lecturer at Lewis School of English Mr Andrew Bourner and Engineer Musaddaq Saeed for their kindness, encouragement and support whenever was necessary.

### **ABSTRACT**

The human brain is one of the most complex systems known to mankind with an estimated 100 billion neurons, 0.15 quadrillion (150 thousand billion) synapses and around a trillion glial cells. Understanding this intricate organism has long been the objective of many scientists and researchers. The motivations for comprehending the human brain can be out of sheer curiosity, to cure diseases (e.g. Alzheimer's and depression) or to build efficient braininspired computers. More recently, progress has been achieved in modelling the role of glia cells, a cell that was not previously recognised as a key player in brain repair. To this end, mathematical models have been developed for predicting the behaviour of cells (neuronal and glia) under stimuli. The models range in complexity from highly rich in detail such as Hodgkin-Huxley to simpler models like Leaky-integrate and Fire (LIF). An artificial neural network is a grouping of neurons in a certain structure such as feed forward. Spiking Neural Networks (SNNs) are the third generation of neural networks and employ the temporal computing abilities of the human brain. Programming languages such as Matlab or Pynn are used to simulate SNNs however, simulations exhibit signification execution times for large networks. The inclusion of astrocytes, a type of glia cell, - in an SNN provides Spiking Astrocyte Neural Network (SANN). Due to the high computational and complexity of astrocytes, SANNs suffer from even further increased execution times.

This PhD research addresses the issue of prolonged simulation times by utilizing dedicated hardware on FPGAs for accelerating SANN simulations. Astrocytes are incorporated into the simulated models to give the SANN the ability to self-repair. Since FPGAs have limited resources, a NoC-based multi-FPGA infrastructure is developed to accommodate SANNs with resource demands exceeding a single FPGA. On top of that, a monitoring and configuration platform is implemented to configure various aspects of the network at the start of operation and to take data off-chip for storage and analysis on a PC during simulations.

The following points summarize the major contributions of this study;

- 1- Developing a new 32-bit fixed-point hardware prototype for biologically faithful astrocyte model.

- 2- Incorporating the astrocyte prototype with hardware models of neurons and synapses to facilitate a self-repairing FPGA-based SANN Accelerator (FSA).

- 3- Designing a novel NoC router, NoC infrastructure and data format to facilitate scalable a multi-FPGA NoC AstroByte platform.

- 4- A novel FPGA Configuration and Monitoring Platform (FCMP) was utilized for injecting faults, configuring the AstroByte platform and capturing real time simulation data for monitoring and analysis on a PC.

# List of Figures

| FIGURE 1:1 ASTROBYTE PLATFORM                                                                                          | 16 |

|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2:1: LIF Circuit model (a) and response (b) [25]                                                                | 22 |

| FIGURE 2:2 TRIPARTITE SYNAPSE [6]                                                                                      | 26 |

| Figure $2:3$ Interactions between the astrocyte and the two neurons between and after faults $[6]$ $\dots$             | 29 |

| Figure 2:4 SPANNER hardware architecture [12]                                                                          | 32 |

| Figure 2:5 H-NoC overall architecture [71]                                                                             | 33 |

| FIGURE 2:6 HANA OVERALL ARCHITECTURE [61]                                                                              | 34 |

| FIGURE 2:7 ASTROCYTE TILE ROUTER [75]                                                                                  | 35 |

| FIGURE 2:8 EMBRACE ARCHITECTURE [10]                                                                                   | 36 |

| FIGURE 2:9: ARCHITECTURE OF THE PROPOSED POLYCHROMOUS SNN [95]                                                         | 37 |

| FIGURE 2:10 A 2-FPGA SNAVA PLATFORM [98]                                                                               | 38 |

| Figure 2:11 Mesh network [3]                                                                                           | 41 |

| FIGURE 3:1 AN OVERVIEW OF ASTROBYTE ARCHITECTURE                                                                       | 46 |

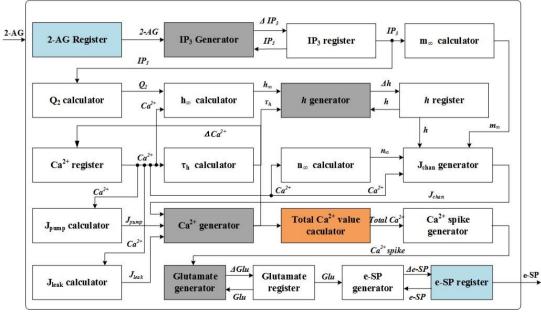

| FIGURE 3:2 ASTROCYTE HARDWARE BLOCK DIAGRAM [13]                                                                       | 47 |

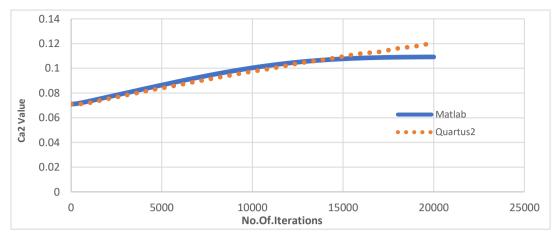

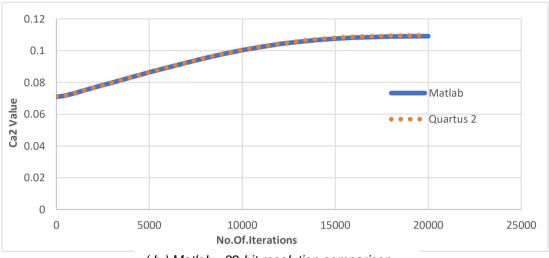

| FIGURE 3:3 COMPARISON BETWEEN THE DOUBLE-FLOAT MATLAB ASTROCYTE MODEL AND ITS FIXED-POINT VHDL HARDWARE IMPLEMENTATION |    |

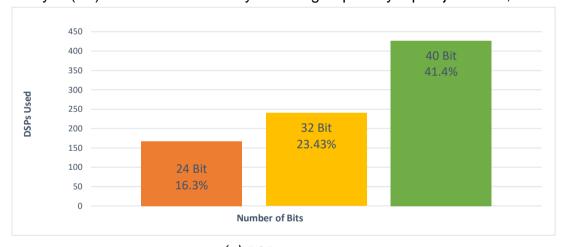

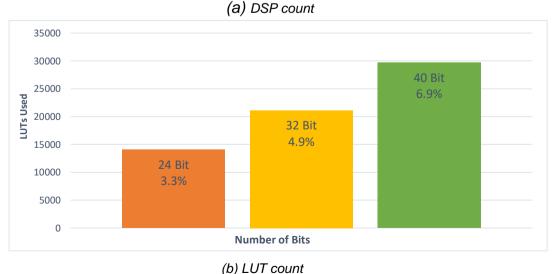

| FIGURE 3:4 COMPARISON OF RESOURCE UTILIZATION BETWEEN THE DIFFERENT ASTROCYTE IMPLEMENTATIONS                          |    |

| FIGURE 3:5 INTERACTIONS BETWEEN THE ASTROCYTE AND THE TWO NEURONS BETWEEN AND AFTER THE FAULT IS INJ                   |    |

| [6]                                                                                                                    |    |

| FIGURE 3:6: FAULT MODELLING ARCHITECTURE IN FPGA HARDWARE                                                              |    |

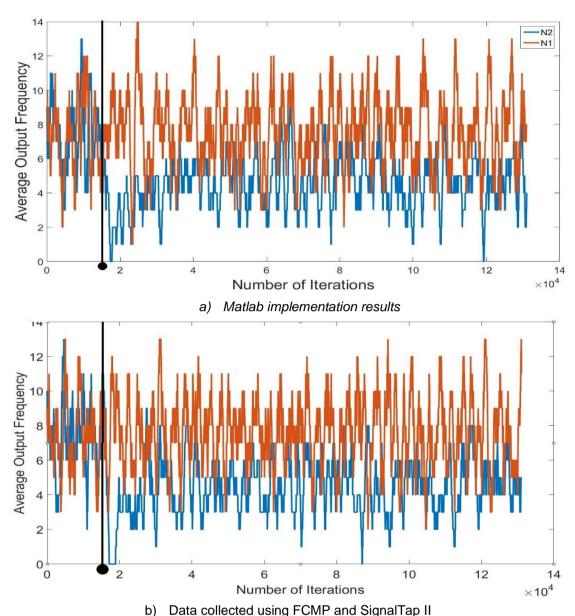

| FIGURE 3:7 AVERAGE OUTPUT FREQUENCIES OF N1 AND N2                                                                     | 53 |

| FIGURE 3:8 AVERAGE NEURON FREQUENCIES IN RESPONSE TO DIFFERENT RATES OF INJECTED FAULTS                                |    |

| FIGURE 3:9 ALGORITHM OUTLINING THE FMP OPERATION                                                                       |    |

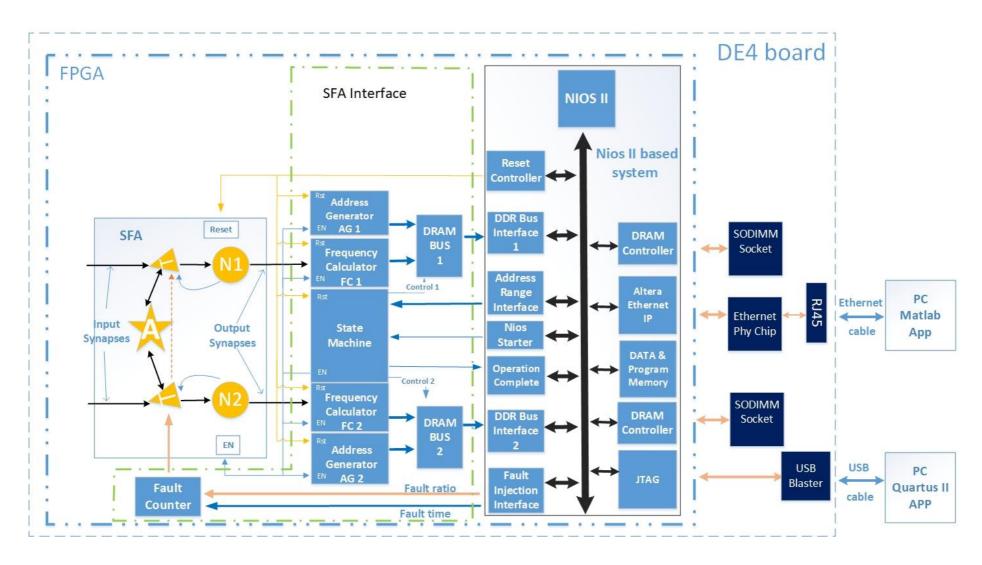

| FIGURE 3:10: FMCP ARCHITECTURE AND FSA                                                                                 | 61 |

| FIGURE 3:11 INTERACTIONS BETWEEN MATLAB, NIOS II AND FSA                                                               | 62 |

| FIGURE 3:12 COMPARISON BETWEEN DATA COLLECTED USING MATLAB AND FCMP                                                    | 63 |

| FIGURE 4:1 AN OVERVIEW OF ASTROBYTE PLATFORM                                                                           | 68 |

| Figure 4:2 Terasic DE4 board                                                                                           | 68 |

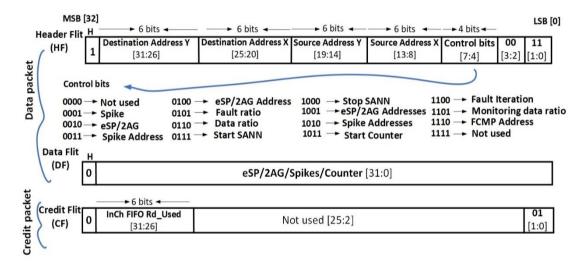

| FIGURE 4:3 AN OVERVIEW OF ASTROBYTE DATA FORMAT                                                                        | 71 |

| FIGURE 4:4 NOC ROUTER OVERALL ARCHITECTURE                                                                             | 73 |

| FIGURE 4:5 ATT HARDWARE BLOCK DIAGRAM                                                                                  | 76 |

| Figure 4:6 ATT pseudo code                                                                                             | 77 |

| FIGURE 4:7 THE ROUTING ENGINE PSEUDO CODE                                                                              | 78 |

| Figure 4:8 Router Xbar architecture                                                                                    | 80 |

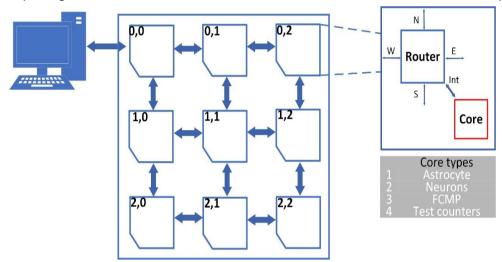

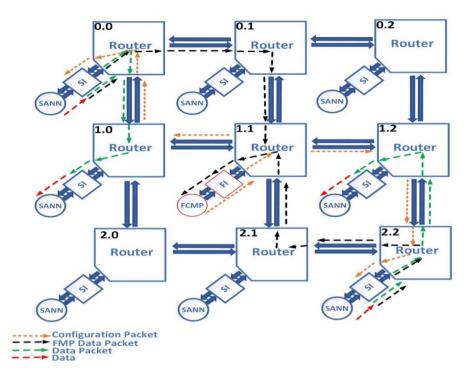

| Figure 4:9 A 3x3 mesh NoC architecture                                                                                 | 83 |

| FIGURE 4:10: FCMP INTERFACE ARCHITECTURE                                                                               | 84 |

| FIGURE 4:11 NIOS II CONFIGURATION DATA PACKETIZATION                                                                   | 85 |

| FIGURE 4:12 ALGORITHM OUTLINING HANDSHAKING AND DATA TRANSFER BETWEEN FCMP AND FI                                      | 87 |

| Figure 4:13 SANN Interface (SI) microarchitecture                                                                      | 88 |

| FIGURE 4:14 ASTROBYTE DATA FORMAT                                                                                      | 89 |

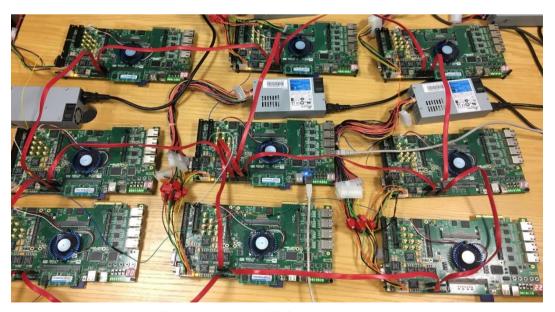

| FIGURE 5:1: A 3x3-FPGA ASTROBYTE PLATFORM                                                                              | 93 |

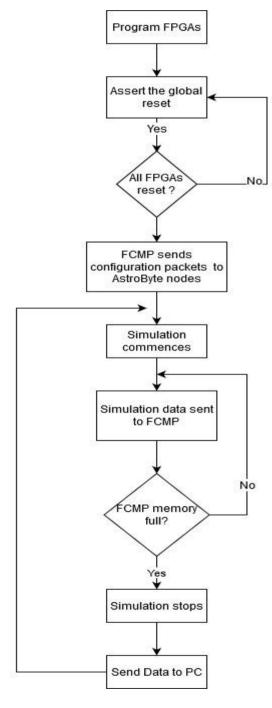

| FIGURE 5:2: ASTROBYTE OPERATION PROTOCOL                                                                               | 94 |

| Figure 5:3 AstroByte setup for configuration, communication and acquisition phases                                     | 95 |

| FIGURE 5:4 ASTROBYTE SETUP FOR THROUGHPUT TEST                                                                         | 96 |

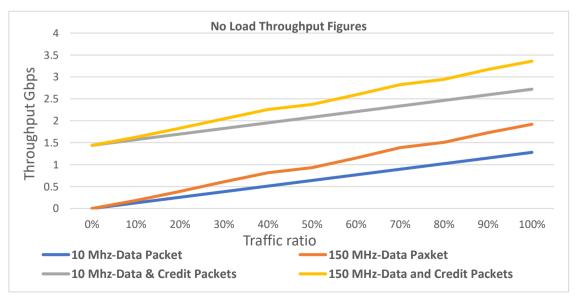

| Figure 5:5: Various Throughput results under no load condition                                                         | 97 |

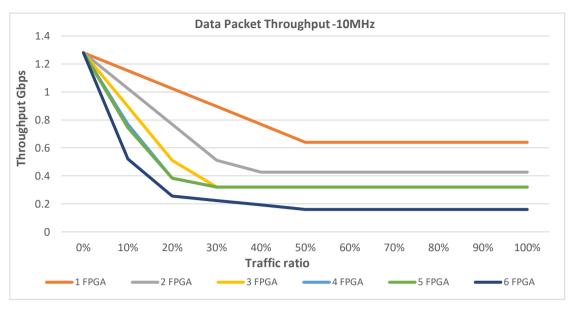

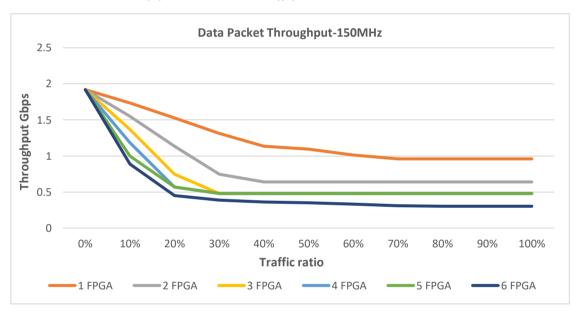

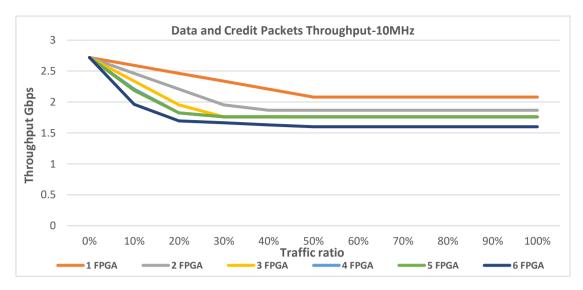

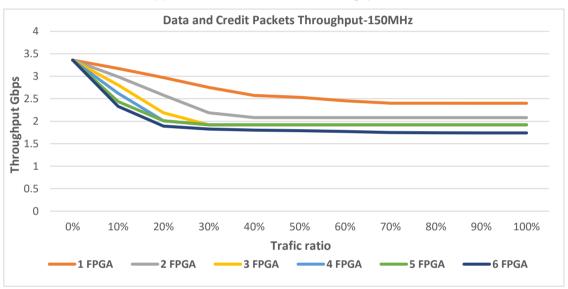

| FIGURE 5:6 DATA PACKET THROUGHPUT FOR 10MHz AND 150MHz                                                                 |    |

| FIGURE 5:7 DATA AND CREDIT PACKET THROUGHPUT FOR 10MHz AND 150MHz                                                      | 99 |

|                                                                                                                        |    |

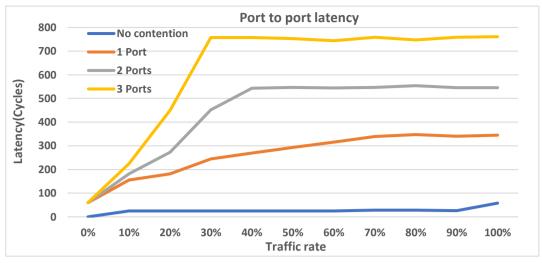

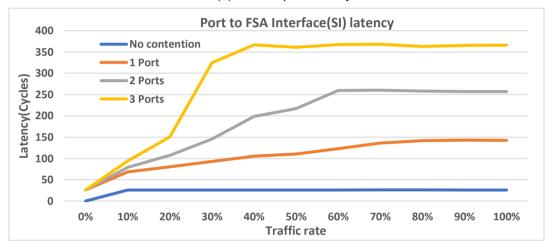

| FIGURE 5:8 LATENCY FIGURES FOR ASTROBYTE PLATFORM                               | 100 |

|---------------------------------------------------------------------------------|-----|

| FIGURE 5:9 PROTOTYPE ASTROBYTE CONFIGURATION                                    | 102 |

| FIGURE 5:10 PROTOTYPE SANN MAPPING ON ASTROBYTE                                 | 103 |

| FIGURE 5:11 ACCURACY COMPARISON BETWEEN ASTROBYTE AND MATLAB                    | 108 |

| <u>List of Tables</u>                                                           |     |

| Table 3:1 Speedup results using different astrocyte implementations             | 55  |

| TABLE 3:2 ACCELERATION GAIN BY USING DRAM                                       | 64  |

| TABLE 3:3 UNDER-SAMPLING EVALUATION                                             | 64  |

| Table 3:4 Acceleration gain by using SRAM at 100 MHz                            | 65  |

| Table 3:5 Acceleration gain by using SRAM at 200 MHz                            | 66  |

| Table 4:1 Programmable attributes of FSA elements                               | 88  |

| TABLE 5:1 UNDER-SAMPLING BY RUNNING SIMULATION FOR 20,480,000 CYCLES            | 101 |

| TABLE 5:2 UNDER-SAMPLING FOR 2x2 FPGA ASTROBYTE BY DECREASING SIMULATION CYCLES | 104 |

| TABLE 5:3 COMPARISON BETWEEN ASTROBYTE AND SOFTWARE IMPLEMENTATIONS             | 104 |

| TABLE 5:4 COMPARISON BETWEEN ASTROBYTE, SNAVA AND BLUEHIVE                      | 111 |

|                                                                                 |     |

# List of acronyms and abbreviations

2-AG 2-Arachidonoylglycerol

AER Address Event Representation

AG Address Generators

ANN Artificial Neural Network

ASIC Application Specific Integrated Circuits

ATT Arbiter Track Table

ATT FIFO Arbiter Track Table FIFO

BCM Bienenstock, Cooper, and Munro

BFT Butterfly Fat Tree

BSTDP BCM-STDP

CB1Rs Type 1 Cannabinoid Receptors

CDR Clock Data Recovery

CE Computing Element

CEI Computing Element Interface

CICR Calcium Induced Calcium Release

CNN Convolutional Neural Network

CPU Central Processing Unit

DCFIFO Dual Clock First In First Out

DDR DRAM Double Data Rate DRAM

DOR Dimension Order Routing

DRAM Dynamic RAM

DSE Depolarization Induced Suppression of Excitation

DSP Digital Signal Processor

e-SP Synaptic Potentiation

EDA Electronics Design Automation

ER Endoplasmic Reticulum

Fault CNTRL Fault controller

FC Frequency Calculators

FCMP FPGA Configuration and Monitoring Platform

FI FCMP Interface

Flit Flow Control Unit

FPGA Field Programmable Gate Array

FSA FPGA SANN Accelerator

GA Genetic Algorithm

Gbps Giga bits per second

GPU Graphics Processing Unit

GXB Gigabit Transceiver Block

H-NoC Hierarchical NoC

HANA Hierarchical Astrocyte Network

HDL Hardware Description Language

HH Hodgkin-Huxley

HSMC High Speed Mezzanine Card

HMI Human Machine Interface

HLS High Level Synthesis

IC Integrated Circuits

ICR Input Controller

ICTT Input Channel Track Table

ICTT FIFO Input Channel Track Table FIFO

InCh FIFO Input channel FIFO

IP Intellectual Property

IP3 Inositol trisphosphate

ISA Instruction Set Architecture

ISC Input Stream Controller

ISRC Intelligence Systems Research Centre

L-Ca<sub>v</sub> L-type Voltage Gated Calcium

LAM Loihi Astrocyte Module

LFSR Linear Feedback Shift Register

LIF Leaky Integrate and Fire

LPDDR Low Power Double Data Rate DRAM

LUT Look Up Table

mGlu Metabotropic Glutamate

mGluR Metabotropic Glutamate Receptor

NGN Neuron-Glial Network

NMDA N-methyl-D-aspartate

NoC Networks-on-Chip

OC Output Controller

OSC Output stream controller

OutCh FIFO Output channel FIFO

PAXY Pseudo Adaptive XY Routing

PC Personal Computer

PR Probability of Release

PRNG Pseudo Random Number Generator

RAC Reward-Attention Coupled

RAM Random Access Memory

RdCNTRL Read Controller

RDC Router Data Controller

RE Routing Engine

RTL Register Transfer Level

SANN Spiking Astrocyte Neural Networks

SATA Serial Advanced Technology Attachment

SCM Single Constant Multiply

SDK Software Development Kit

SDRAM Synchronous DRAM

SERCA Sarco-Endoplasmic-Reticulum

SI SANN Interface

SM State Machine

SNN Spiking Neural Networks

SoC System on Chip

SRAM Static RAM

STDP Spike Timing Dependent Plasticity

SXYR Surrounding XY Routing

TDM Time Division Multiplexing

TRNG True Random Number Generator

UART Universal Asynchronous Receiver/Transmitte

VHDL Very High-Speed Integrated Circuit HDL

WrCNTRL Write Controller

Xbar Crossbar

# Chapter 1: Introduction

In this chapter, a brief background will be provided regarding the major scientific and engineering concepts that have been utilized in the PhD research. The key objectives, motivation and challenges of the research will also be presented.

#### 1.1 Background

This research project is multi-disciplinary in nature incorporating the fields of brain-inspired computing, FPGA hardware and Networks-on-Chip (NoC) strategies. The major motivation behind this study is leveraging the flexibility provided by FPGA devices to reduce the simulation times of large SANNs to enable carrying out these simulations in a time-efficient manner. The PhD addresses the challenge of scalable acceleration of SANN applications on FPGA hardware. Achieving large-scale parallel simulations of such systems introduces two major challenges. First, establishing dedicated hardware that faithfully mimic complex biological processes, such as astrocytes, requires a significant amount of hardware resources [1], meaning that the design has to incorporate multiple FPGAs. Second, the challenge of communicating both spike event (neuron data) and numeric (astrocyte data) across significant interconnect pathways between astrocytes and neurons, requires an appropriate hardware communication mechanism. The NoC interconnection paradigm is a communication mechanism suitable for tackling the interconnect challenge. NoCs allows for massive parallel structures in hardware that facilitate a great number of computing nodes, while maintaining throughput performance under node scaling conditions [2], [3].

The following sub-sections provide a brief introduction for explaining Brain-inspired Computing, NoC paradigm and FPGAs.

#### Brain-inspired Computing

In traditional Von Neumann computer architectures, programs are stored in a memory and are fetched and executed sequentially by a central processing unit This type of computers have functioned well so far but are facing major challenge in terms of power consumption and scalability. Brain-inspired Computing is seen as a potential replacement for traditional Von Neumann architectures[4]. This new trend in research is motivated by the fact that biology, in particular the human brain, is able to perform computations more efficiently in terms of power consumption, more robust to failures, and in a massively parallel manner. lately, SNNs have been seen as a modern way to create such brain-like computing systems [5].

The ability of the human brain to perform self-repair is another significant feature that electronic systems designers are keen to mimic in the next generation of computer systems. It has been put forward lately that a specific

type of glial cell, namely the Astrocyte, is a key player in self-repair as it is now believed they have an important role in modulating synaptic activity by mediating direct and indirect feedback to presynaptic and postsynaptic neurons [6], [7]. The interactions between astrocyte and neuron cells facilitates a distributed self-repair capability.

Astrocytes enwrap groups of tripartite synapses and therefore are able to communicate with presynaptic and postsynaptic neurons at synaptic junctions [6], [8]–[10]. The SANN [11] is the addition of astrocyte cells in the current SNN paradigm. Because of the astrocyte inclusion, SANNs introduce significant computational complexity along with higher exchanges of data. Previous work at Ulster has developed a small hardware demonstrator of a spiking astrocyteneuron network [12], [13], however, progress needs to be made in developing a method of accelerating the simulation of large-scale SANNs in hardware.

#### Networks-on-Chip

Networks-on-Chip is an interconnection centric paradigm with a scalable infrastructure that can host a wide variety of subsystems and Intellectual properties (IPs). NoC is the answer for current bus-based architecture bottlenecks in terms of scalability, performance and efficiency. As the number of Computing Elements (CE)s are ever increasing in modern computing systems, sharing a single bus introduces many problems [2], [14]–[17]. NoC replaces highly dense point to point connections with an internet like structure.

#### FPGAs

Field Programmable Gate Arrays (FPGAs) are reconfigurable hardware that through a programmable interconnection structure and Look Up tables (LUTs) give the designers the ability of changing the implemented logical function when necessary [18]–[20]. This flexibility has made FPGA extremely convenient for use in research environments and in applications where hardware reconfigurability is an advantage. Modern FPGAs can work at frequencies of over 500MHz with complete digital systems now able to reside on the largest, high-end devices. Furthermore, beside the reconfigurable elements, modern FPGAs contain specialized elements such as Digital Signal Processors (DSPs), embedded processors and high-speed transceivers. Therefore, FPGAs have found their way into many industrial applications such as aerospace, ASIC prototyping and automotive [21].

#### 1.2 Motivation

Prior work within the research team at Ulster has demonstrated the astrocyteenabled brain-inspired self-repair principle in hardware using floating-point implementations [12]. Implementing such SANNs in hardware allows for future computing tasks to self-repair in the presence of hardware failure; thereby providing high degrees of reliability. One key focus and contribution of this work is the feasibility of implementing such mechanisms on FPGAs using reduced fixed-point representation, where biologically realistic accuracy can still be maintained. In this context, current research in self-repair has focused on astrocytes, which is the mechanism responsible for facilitating fine-grained self-repair. These SANNs modulate the synaptic activities between neurons via distributed astrocytes in the network. This concept was proven in previous work when an astrocyte was integrated with an SNN [6]. Due to the complex mathematical nature of the astrocyte model in previous work [6], simulating the SANN using tools such as Matlab required long execution times, in particular as the astrocyte is not event based like traditional SNNs and operates over longer biological timescales of hundreds of seconds. This motivated the need for designing an FPGA-based SANN Accelerator (FSA) platform for accelerating simulations of SANNs through implementing dedicated astrocyte, neuron and synapse hardware models on FPGAs [1].

To facilitate experimentation, a framework was required to enable fault injection, spike/astrocyte data recording and visualization of FPGA-based SANNs. Current on-chip mechanisms such as Intel SignalTap II Logic Analyzer are not adequate as their capacity is limited by the amount of on-chip memory afforded by the FPGA.

This is the motivation for designing a platform that enables configuration of the accelerator SANN- the FSA, injecting faults and sending monitoring data to a PC for analysis and storage. The FPGA – based Configuration and Monitoring Platform (FCMP) forms the second contribution of this research and is used for injecting configuration packets at the start and then collecting monitoring packets during the FSA running time.

Accelerating simulations of massive SNNs necessitates dedicating significant FPGA resources for their implementations. The inclusion of astrocytes, especially biologically faithful ones as in this work, into spiking neural networks, dramatically increases hardware Furthermore. FPGA usage. communication demands increase as two types of data, namely spikes (from neurons) and astrocyte data, have to be exchanged. Thus, accelerating largescale SANNs calls for novel approaches beyond single-FPGA shared bus utilizations. This interesting challenge has motivated the third contribution of this work, which is designing a programmable multi-FPGA NoC-based infrastructure that is capable of accommodating large numbers of astrocytes, tripartite synapses and the two-fold communications neurons and requirements.

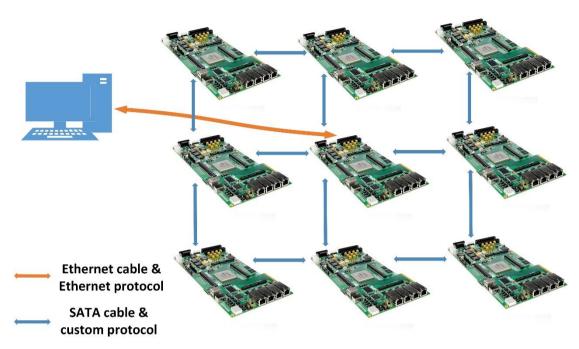

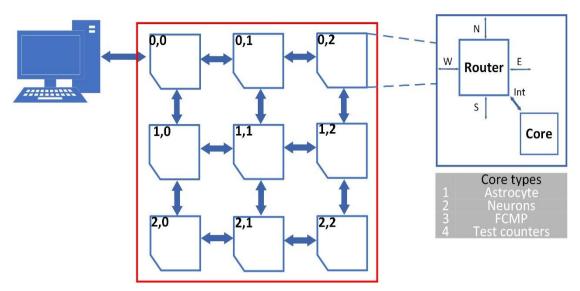

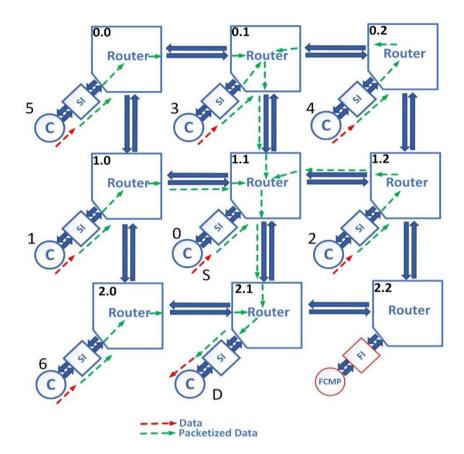

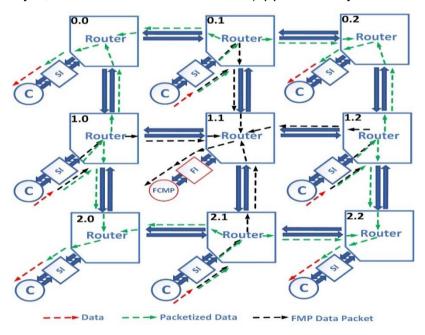

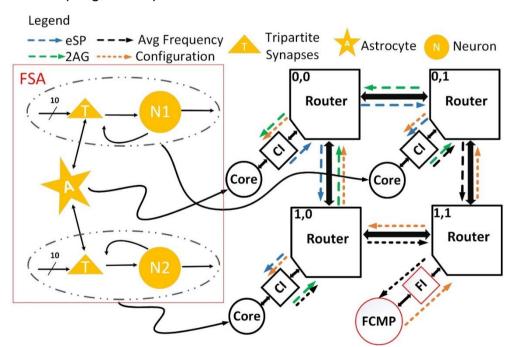

AstroByte, illustrated in Figure 1:1 is a single platform that integrates all the above-mentioned contributions. It uses the FSA as its computing element, FCMP as its core component for injecting configuration packets and collecting data for analysis, and the multi-FPGA NoC structure for providing data communication infrastructure for massive parallel SANNs. AstroByte can have any number of nodes, Figure 1:1 shows an example 3x3 AstroByte platform.

Figure 1:1 AstroByte platform

#### 1.3 Thesis Hypothesis and Contributions

The main hypothesis of this research is that dedicated FPGA hardware can accelerate SANN simulation. The main task of this research is to prove that both spikes, which are discrete in nature, and astrocyte data, which is continues, can be generated concurrently in the same system. Furthermore, this work proves that efficient interconnection mechanism and data format can make a NoC to support both continues and discrete data exchange. Additionally, this study acts as evidence that despite NoC interconnection and data monitoring overheads, a multi-FPGA SANN platform can retain functional accuracy while providing up to x188 speedup when compared to an equivalent software model of the SANN. As will be become clearer in chapter 2, there is a gap in the literature regarding large-scale implementation of self-repairing SANNs that incorporate both continues and discrete computations for self-repair.

Below is the list of the major scientific and technical contributions springing from this research.

1- A novel fixed-point hardware prototype for a biologically faithful astrocyte model [6] was developed with an appropriate numerical representation type and bit resolution. Results demonstrate that the astrocyte accuracy is comparable to equivalent software implementations. This contribution allows for building SANN FPGA Accelerators with high accuracy while reducing hardware footprint when compared to floating point implementations.

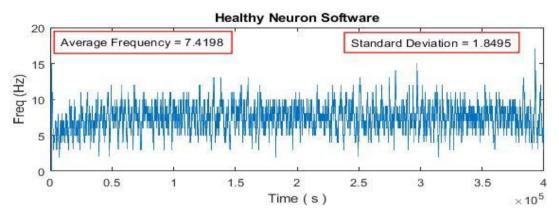

- 2- The new astrocyte hardware was Integrated with neurons and synapses to facilitate an FPGA-based SANN Accelerator (FSA). Results indicate that accelerations of more than x1000 has been achieved and high accuracy was maintained in terms of neurons firing frequency when compared to equivalent Matlab models. This proves that FPGA accelerations can save researchers in the field of computational brain modelling a great deal of time.

- 3- A novel FPGA Configuration and Monitoring Platform (FCMP) was utilized for injecting faults, configuring the AstroByte platform and capturing real time simulation data for monitoring and analysis on a PC. The FCMP helps bypassing the limitations of data collection of tools like SignalTap II in terms of the amount of data that can be monitored. Additionally, through the FCMP platform the user can change some attributes of the FPGA design without re-synthesizing the design, allowing for more time-efficient simulations.

- 4- New controllers for high-speed serial transceivers to allow transmission of data between FPGA boards were developed, making way for large scale, highly parallel multi-FPGA SANN implementations.

- 5- A new NoC router was developing that can function with the transceiver controllers to realize scalable multi-FPGA NoC infrastructure.

- 6- Novel protocols were designed for ensuring integrity of data transformation between FPGA boards, as well as the NoC router and AstroByte components. This allows for maintaining the accuracy and integrity of simulations while large scale SANNs are mapped to the multi-FPGA NoC structure.

#### 1.4 Thesis Outline

Chapter 2 provides a literature review and starts by discussing neuron models and then moves onto investigating astrocyte and tri-partite synapse models. The chapter summarizes the significant works regarding astrocyte hardware utilizations, both in-house models and others, together with the interconnection methods for astrocytic signalling in hardware. In addition, the main literature regarding SNNs are investigated and the most state of the art in the domain of ASIC implementations of SNNs are reviewed.

Chapter 3 starts with introducing a novel FPGA SANN Accelerator (FSA) that has a biologically faithful astrocyte at its core, forming the first contribution of this work. A reduced fixed-point representation of the astrocyte process is implemented and discussed in detail. To strike a balance between FPGA resource usage and accuracy, different bit resolutions are tried and the appropriate one is chosen. In addition to that, the ability of FSA to perform self-repair when exposed to various levels of faults is proved. Furthermore, high accuracy is maintained when weighed up against an identical Matlab model. In addition, the chapter provide comparisons between acceleration due to utilizing a SANN model on dedicated FPGA hardware and a similar Matlab implementation.

The second contribution of this research is a configuration and monitoring platform, called FCMP. The chapter evaluates the architecture and operation of FCMP in detail by providing thorough descriptions regarding each of FCMP components. The operation of the platform and the interactions between a Nios II embedded processor system and custom hardware are analysed. Data integrity is assessed by comparing data collected using Intel SignalTap II and the FCMP. The new acceleration data from the result of integrating FCMP with the SANN hardware are presented as well. Chapter 3 also examines methods to enhance FCMP performance and overall acceleration along with showing new acceleration figures as the result of these improvements.

Chapter 4 presents the AstroByte platform's multi-FPGA NoC infrastructure by means of detailed explanation of the AstroByte NoC data format, router architecture, operation and the logic blocks forming the router. Additionally, AstroByte programmability and the design choices that allow for this flexibility are investigated. Furthermore, the FCMP Interface (FI) and the SANN Interface (SI) blocks that allow smooth communication between the NoC router and the FSA or the FCMP are discussed. FCMP from *Chapter* 3 is adapted for proper interfacing with the router through FI.

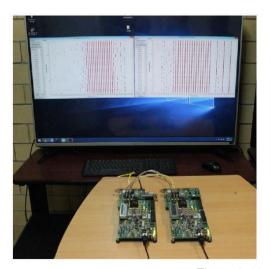

Chapter 5 presents results and the experiment setup that was used throughout. The chapter introduces the example 9-FPGA AstroByte platform configuration used for collecting results on throughput and latency. Additionally, a prototype AstroByte platform is used to test the features in terms of simulation, undersampling and data acquisition. A subsequent section deals with integrating the SANN accelerator (FSA) on a 2x2 FPGA AstroByte configuration. Figures regarding speedup factors, at different under-sampling rates, and accuracy are showcased. In addition, AstroByte is compared against two other (relatively) similar platforms, SNAVA and Bluehive, in regard to features and capabilities.

Chapter 6 is the thesis conclusion which includes a section discussing future works and another for self-critic.

#### 1.5 Publications

The list of the outcome publications from this work are given below:

#### Papers I have published as the first author:

1- S. Karim et al., "FPGA-based Fault-injection and Data Acquisition of Self-repairing Spiking Neural Network Hardware," in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 2018, pp. 1–5.

(The work originates from Chapter 3)

2- S. Karim et al., "Assessing Self-Repair on FPGAs with Biologically Realistic Astrocyte-Neuron Networks," in Proceedings of IEEE Computer Society Annual Symposium on VLSI, ISVLSI, 2017, vol. 2017-July, pp. 421–426.

(The work originates from Chapter 3)

3- S. Karim et al., "AstroByte: A multi-FPGA Architecture for Accelerated Simulations of Fault-tolerant Spiking Astrocyte-Neuron Networks," in Proceedings of IEEE Design, Automation & Test in Europe, DATE, 2020 (Accepted- a virtual conference is planed pending confirmation of the date).

(The work originates from Chapters 4 and 5)

#### Other papers in which I contributed to include:

- 4- A. P. Johnson et al., "Fault-Tolerant Learning in Spiking Astrocyte-Neural Networks on FPGAs," in 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), 2018, pp. 49–54.

- 5- J. Liu et al., "Self-repairing Learning Rule for Spiking Astrocyte-Neuron Networks," Lecture Notes in Computer Science, Springer 2017, pp. 384–392.

- 6- A. P. Johnson et al., "Homeostatic Fault Tolerance in Spiking Neural Networks: A Dynamic Hardware Perspective," IEEE Trans. Circuits Systems I: Regular. Paper, vol. 65, no. 2, pp. 687–699, Feb. 2018.

- 7- A. P. Johnson et al., "Homeostatic fault tolerance in spiking neural networks utilizing dynamic partial reconfiguration of FPGAs," in 2017 International Conference on Field Programmable Technology (ICFPT), 2017, pp. 195–198.

- 8- J. Liu et al., "Self-repairing Learning Rule for Spiking Astrocyte-Neuron Networks," Springer, Cham, 2017, pp. 384–392.

- 9- A. P. Johnson et al., "An FPGA-based hardware-efficient fault-tolerant astrocyte-neuron network," in 2016 IEEE Symposium Series on Computational Intelligence (SSCI), 2016, pp. 1–8

# Chapter 2: Literature Review

This chapter outlines the most important and relevant literature in the domain of this work. The main models available for both neurons and astrocytes will be discussed. The review will highlight the dynamics and equations of the astrocyte model that enables SNNs to perform self-repair. Current research progress in FPGA implementations of SNNs will be reviewed along with the state of the art in astrocytes hardware implementations. In addition, the chapter reviews efforts in establishing astrocyte communications using the NoC paradigm. Particular attention will be given to the SNN hardware architectures that are comparable to the multi-FPGA architecture implemented in this work.

#### 2.1 Neuron Models

As a vital component for both understanding and modelling the human brain along with construction of neural networks, quantifying neurons behaviour has been the subject of intensive research during the last six decades. Rosenblatt's perceptron model [22] is considered to be the first neuron model that has the ability of forming a neural networks to perform semi-autonomous tasks through supervised learning. Since then, the field of neuron modelling and neural networks has gained much attention in the scientific community for various purposes e.g. machine learning, computational modelling of the brain and power efficient computing.

As neurons are the fundamental elements in neural networks, this section discusses the most widely used models available in the literature.

#### 2.1.1 Hodgkin-Huxley (HH) Model

This is one of the most famous models as regards quantitatively reproducing neural action potentials [23]. This model takes into consideration the dependency of sodium, potassium and leak current on the membrane potential. Results gained from experiments show that this model can accurately represent action potentials together with the membrane voltage threshold and refractory periods in biology cells. The current through the cell membrane is given by

$$I = Cm\frac{dVm}{dt} + \bar{g}_K n^4 (V_m - V_K) + \bar{g}_{Na} m^3 h(V_m - V_{Na}) + \bar{g}_l (V_m - V_l)$$

(1)

where

$$\frac{dn}{dt} = \alpha_n (V_m)(1-n) - \beta_n(V_m)n \tag{2}$$

$$\frac{dm}{dt} = \propto_m (V_m)(1-m) - \beta_m(V_m)m \tag{3}$$

$$\frac{dh}{dt} = \propto_h (V_m)(1-h) - \beta_h(V_m)h \tag{4}$$

Where I is the total current of the membrane,  $C_m$  represents the membrane capacitance,  $\bar{g}_k$ ,  $\bar{g}_{Na}$  and  $\bar{g}_L$  are potassium, sodium and leak maximum conductance, respectively. All the above-mentioned variables are per unit area.  $V_I$ ,  $V_K$  and  $V_{Na}$  are leak, potassium and sodium reversal potentials respectively.  $V_m$  is the membrane potential while  $\propto_x$  and  $\beta_x$  are rate constants belonging to ion channel x. n and m are dimensionless quantities with values of either 1 or 0 relating to activation of potassium and sodium channels correspondingly and h is of a similar nature as n and m but associated with inactivation of sodium channels. The HH model reproduces biological properties of membrane cells faithfully. However, it requires a great deal of computational power and for this reason simpler neuron models are generally used for modelling SNNs.

#### 2.1.2 Pinsky-Rinzel Model

This is a non-linear two compartment neuron model in which the soma and dendrite are modelled in two separate compartments [24]. The equations of this model are as follows: -

$$Cm\frac{dV_S}{dt} = -\bar{g}_L(V_S - E_L) - g_{Na}(V_S - E_{Na}) - g_{DR}(V_S - E_K) + \frac{g_C}{P}(V_d - V_S) + \frac{IS}{P}$$

(5)

$$Cm\frac{dV_d}{dt} = -\bar{g}_L(V_d - E_L) - g_{Ca}(V_d - E_{Ca}) - g_{AHP}(V_d - E_K) - g_C(V_d - E_K) + \frac{g_C}{1-P}(V_S - V_d) + \frac{I_{Syn}}{1-P}$$

(6)

Where  $I_s$  is the current applied to soma and p is the percentage area occupied by the soma.  $E_L$ ,  $E_{Ca}$ ,  $E_{Na \text{ and}}$   $E_K$  are respective leakage, Calcium, Sodium and Potassium equilibrium (reverse) potentials.  $\bar{g}_L$ ,  $g_{Na}$ ,  $g_{DR}$   $g_{Ca}$ ,  $g_{AHP}$  and  $g_c$  are leakage, Sodium, Potassium delayed rectifier, Calcium, Potassium (afterhyperpolarization) and coupling conductance, respectively.  $I_{Syn}$  is the synaptic current. Although the model uses only two compartments, it can replicate a wide range of realistic activity patterns that are created as a result of accurate injection of current through the soma or dendrite compartments [25].

#### 2.1.3 FitzHugh-Nagumo Model

This model is a simplified form of the HH model. Richard Fitzhugh reduced the four equations describing the HH model to a two-dimensional form by making several observations and reductions regarding the gating variables *n*, *m* and *h*. The final equations adopted by this model are given below:

$$\frac{dv}{dt} = v(v - \alpha)(1 - v) - w + I \tag{7}$$

$$\frac{dw}{dt} = \varepsilon(v - \gamma w) \tag{8}$$

Where v represented the potential (fast variable) and w is the slow variable (gating variable of sodium). Other symbols, namely  $\propto$ ,  $\varepsilon$  and  $\gamma$  are constants

[26]. The FitzHugh-Nagumo model is also referred to as a single compartment model [25].

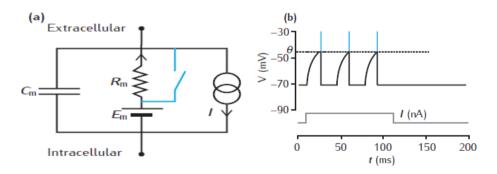

#### 2.1.4 Leaky Integrate and Fire Neurons

The Leaky Integrate-and-Fire (LIF) neuron is capable of reproducing firing of spikes (action potentials) when the membrane potentials level passes a certain threshold. This model can be represented by means of an RC circuit as shown in Figure 2:1.

$$C_m \frac{dV}{dt} = -\frac{Vi - E_m}{R_m} + I \tag{9}$$

Where  $R_m$  represents the membrane resistance,  $C_m$  is the membrane capacitance and I is the cellular current. Other variants of integrate-and-fire neurons also exist, such as Quadratic integrate and fire model [25].

This study uses this model for accelerating SANN simulations with FPGAs for two reasons. Mainly, despite its simplicity, LIF model can reproduce the basic characteristics of neurons that are necessary for SNN implementation in an efficient manner. In fact, LIF model is used widely in SNN literature because the model does not require a lot of computational resources. For this work, the characteristics that LIF can reproduce is enough for assessing the AstroByte platform and its capabilities in terms of acceleration, accuracy etc, nullifying the need of using more area and power-hungry models. Additionally, the hardware implementation of SANN in this study will be compared against an equivalent in-house built Matlab model for assessing accuracy and speed of Astrobyte. The Matlab model implements LIF model, necessitating choosing LIF for the equivalent hardware model to permit comparisons between the two models. An alternative approach would be changing the neuron model both in the Matlab model and AstroByte, however one can't justify spending such extra effort giving that the LIF model can adequately simulate self-repairing SANNs.

Figure 2:1: LIF Circuit model (a) and response (b) [25]

•

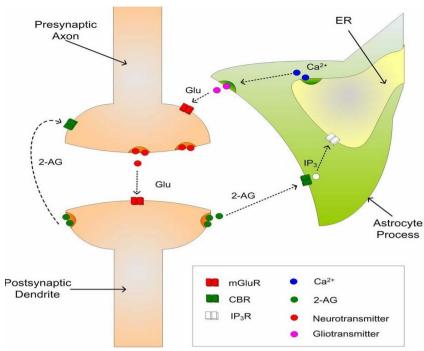

#### 2.2 Astrocyte and Tripartite Synapse

Astrocytes are a type of glial cell found in the human brain in large quantities. It is estimated that their numbers outweigh that of neurons by 10:1 and amass around 25%-50% of the total brain volume. Contrary to neurons, astrocytes do not have axons and are unable to output action potentials. Despite the fact that the existence of astrocytes has been known for a long time, their functionality was not understood as they were thought to only provide structural support to neurons. Recent findings, however, indicate that astrocytes contribute to synaptic activity modelling and metabolic interactions with neurons [6], [27]. Astrocytes are able to interact with neurons via the tripartite synapse. At a tripartite synapse junction, an astrocyte process surrounds both presynaptic and postsynaptic terminals (Figure 2:2) enabling the astrocytes to monitor and regulate synaptic activity between the presynaptic and postsynaptic neurons. Moreover, astrocytes are able to communicate to each other through propagation of IP3 (Inositol trisphosphate) and calcium waves [6], [9], [28], [29]. Although there is a form of consensus in the literature regarding the fact that astrocytes observe and modify synaptic activity, the exact mechanisms of this process are interpreted differently in the available publications. In the following sections, we study some of these models.

#### 2.2.1 Astrocyte Models

The Gatekeeper model [30] views the astrocyte as a gatekeeper that controls the spiking rate of the presynaptic terminals that fire constantly and frequently. Astrocyte Intracellular calcium levels are affected by synaptic activity since Metabotropic Glutamate (mGlu) receptors located on astrocytes can sense such activities and lead to an increase in the concentrations of IP3. The Gatekeeper model uses the Li-Rinzel model in which IP3 levels increase upon release of neurotransmitters and causes IP3 mediated calcium release in the astrocyte cell [31].

In addition to the Gatekeeper model, other astrocyte formulae regarding their impacts on both presynaptic and postsynaptic neurons can be found in the literature. A model developed by Nadkarni and Jung [32] has expressed astrocytes as synaptic activity enhancers, in contrast to the Gatekeeper model discussed above. In this model astrocyte activity results in synaptic potentiation. Here, glutamate emitted by astrocytes balances calcium in the presynaptic axon. The source of this calcium is different from that released as a result of the application of a voltage to the presynaptic terminal since it correlates with the astrocyte in terms of timescale. The overall effect is improving the probability of neurotransmitter release following an action potential.

Other astrocyte models have focussed on the function of astrocytes in neural networks. Guimarães et al [33] has investigated using astrocyte for stimulating the impact of nicotine on attentional focus. The upshots of tripartite synapses absorbing glutamate imitated from astrocyte is investigated. Also, the research

addresses the significant capacity of astrocytes to regulate neural response throughout a Reward-Attention Coupled (RAC) circuit [34]. The RAC combines thalamocortical and reward circuitry to look into how nicotine affects attention focus. To this effect, a mathematical model has been developed to represent the mechanism of interactions between the reward and thalamocortical circuits. Simulations of the mathematical model have been carried out that show the interactions between an astrocyte and the RAC circuit and vice versa. The authors have come to conclusion that astrocytes enhance neural network transmissions. Deemyad et al [35] has investigated the relationship of astrocytic calcium activity with neuronal barrage firing [36], [37]. The authors have reported two main evidences for this phenomenon. Firstly, they have reported that barrage firing can still be observed in mice despite lacking necessary units for inducing electrical signals between neurons. The authors see this as evidence that astrocytes, through numerous connections at synaptic gap, could be the initiators of barrage firing. Secondly, inhibiting of barrage firing can be observed by deconcentrating extracellular calcium or closing L-Ca<sub>V</sub> (L-type voltage gated calcium) channels. In contrary, buffering calcium in interneurons does not inhibit barrage firing. The authors have summarized that mechanisms of neural networks, both special and temporal, are being influenced by astrocytes through direct integration of neuronal activity and driving barrage firing some populations of inhibitory interneurons.

Astrocytes have also been used to increase firing rate at tripartite synapses. In Abed et al [38], the internal calcium pool of the astrocyte is being excited by two mechanisms. The first one is a fast mechanism that is initiated by depolarization in postsynaptic neuron. The second one is a slow mechanism which is initiated by presynaptic diffusion. Both these values add to calcium volumes inside the astrocyte. Once a threshold is reached, an astrocyte mediator is emitted that affects the synaptic terminal and increases the possibility of firing in the postsynaptic terminal. Improved firing rate has also been investigated in a theoretical study of the reasons behind unusual (extremely high or low) levels of gliotransmitters at synaptic connections exists [39]. The aim is to remotely keep gliotransmitters concentration levels by means of improving performance of the molecular communications that facilitate Ca<sup>2+</sup> signalling.

Other publications have integrated astrocytes into neural networks for improving the networks ability to solve classification problems. In one of such study, an artificial neuron-glial network (NGN) has been developed and used for solving classification problems [40]. The astrocyte in this model is stimulated when the associated synaptic junction experiences neural activity for a minimum of x out of y iterations (4 out of 6, for example). When the astrocyte is active the synaptic weights increase by 25%, otherwise they decrease by 50%. The authors report that the NGN performance is significantly higher than that of traditional neural networks. Furthermore, astrocytes have been used in artificial NGNs to automate the generation of the values that are usually considered as constant parameters in neuron-glial models. Each neuron is connected to an

astrocyte in this model and improvements have been reported over traditional Artificial Neural Networks (ANNs) and other NGNs in terms of solving classification problems [41].

This section discussed the most prominent astrocyte models (e.g. The Gatekeeper and Nadkarni and Jung models). Further models of astrocytes were discussed to cite some of the usages of astrocytes in the literature. Finally, two review articles will be cited that contain more models of astrocytes, their calcium dynamics and their interactions with neurons [42], [43].

#### > SPANNER & In-house Models

The SPANNER project explored the association between astrocytes and neurons to develop the next generation of algorithms and hardware with the capability of fine-grain fault-tolerant systems [44].

This section discusses the state-of-the-art research in astrocyte modelling and their internal dynamics that have been developed at *Intelligent Systems Research Centre* (ISRC).

Liu et al [45] proposes a biophysical model for reproducing presynaptic and postsynaptic neurons, A Gamma AminoButyric Acid (GABA) interneuron and an astrocyte. According to this model, astrocytic release of calcium from IP3 pathways is triggered by GABA produced by GABA interneurons. In turn, the presynaptic transmission probability rate increases which leads to weight potentiation as well as an incremental uptake in postsynaptic spiking activity before stabilising. The authors have proven that IP3-probability rate interactions cause burst-firing at postsynaptic neurons before the initial phase of weight potentiation.

Moreover, an astrocyte model with BSTDP learning rule has been reported [46]. It combines Spike Timing Dependent Plasticity (STDP) [47] and Bienenstock, Cooper, and Munro (BCM) [48] rules (hence the name BSTDP). In this model, postsynaptic neuron activity participates in potentiation of synaptic weight along with temporal dissimilarity between presynaptic and postsynaptic neurons firing times. It is proven that the height of plasticity window is governed by BSTDP that results in the formation of mapping of inputs to outputs during the learning phase as well as keeping the mapping through self-repair in case synaptic pathways become defective. The real-time self-repairing capabilities of the proposed SANN is affected by the influence of the plasticity window height on the firing activity of postsynaptic neurons. The self-repairing attribute of the SANN has been demonstrated through an obstacle avoidance application on a robotic platform. Furthermore, the reported simulation results reveal that despite fault ratios of up to 80% (not affected by fault location) the SANN maintains its learning manoeuvres.

Modelling glutamate transporters of astrocytes has been explored in a different study [49]. Experimental data and thermodynamics fundamentals have been used to derive an explicit model for glutamate transporters of astrocytes,

Figure 2:2 Tripartite synapse [6]

focussing on glutamate-induced chemical potential on astrocyte membranes. The model shows that uptake in glutamate as a result of synthetize downregulation of glutamine causes postsynaptic quantal size because of gliotransmission. Also, the proposed model indicates that higher astrocytic glutamate levels could increase the time course of glutamate in synaptic cleft and modifies the slow currents produced by the astrocyte. This leads to uptake in frequency of postsynaptic junction and disturbing synaptic signalling.

#### 2.2.2 An Astrocyte Model for Self-repairing Hardware

Research at the *Intelligent Systems Research Centre* (ISRC) has led to an astrocyte model specific to performing self-repair in SANNs. This model will be investigated in more detail than the others since it is used in this work for realizing an astrocyte module in hardware.

The self-repair mechanism focuses on the interactions between astrocyte and neurons. The Ulster model for astrocytes operates within a feedback loop where the activity of neurons is relayed back to their associated synapses via astrocytes [3], [5], [19], [50].

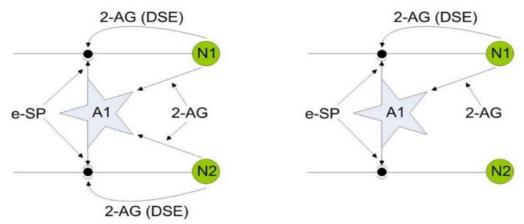

This self-repair mechanism is illustrated in Figure 2:2. When a synapse fails to release neurotransmitter, the associated neural activity falls and consequently the level of 2-AG decreases. The absence of the 2-AG signal, which is a retrograde feedback messenger from active postsynaptic neurons, causes an overall increase in PR at all tripartite synapses. This is because the direct feedback of 2-AG to the presynaptic terminal DSE has diminished leaving the indirect feedback signal from the astrocyte e-SP to cause a sudden increase in PR. It is important to note that one or more nearby active neurons will be sufficient to maintain the astrocyte in an excited state. Therefore, the repair-

capability can be viewed as distributed whereby the state of neurons is continually monitored locally by the nearby astrocyte. Also because the astrocyte coverage is up to about 10<sup>5</sup> synapses then local in biological network terms can be anything between 4 to 12 neurons [51]. The equations representing the self-repairing mechanism in the astrocyte and neuron models are given in equations (10)-(27).

Whenever the postsynaptic neuron fires, an amount of 2-AG is released and can be represented using the following equation:

$$\frac{d(AG)}{dt} = \frac{-AG}{\tau_{AG}} + r_{AG} \delta(t - t_p) \tag{10}$$

Here, AG is the volume of available 2-AG,  $\tau_{AG}$  and  $r_{AG}$  are the decay rate and production rate of 2-AG, respectively. IP3 can be modelled by:

$$\frac{d(IP3)}{dt} = \frac{IP3^* - IP3}{\tau_{ip3}} + r_{ip3} AG \tag{11}$$

where  $\tau_{ip3}$  and  $r_{ip3}$  are IP3 decay and production rates, consecutively and  $IP3^*$  is the initial level of IP3. This change in IP3 quantity can trigger calcium release which is given by [31]:

$$\frac{d(Ca^{2+})}{dt} = J_{chan} - J_{pump} + J_{leak}$$

(12)

Here,  $J_{chan}$  is the IP3 and  $Ca^{2+}$  dependent calcium release,  $J_{pump}$  is the quantity of  $Ca^{2+}$  pumped into the Endoplasmic Reticulum (ER) and  $J_{leak}$  is the total  $Ca^{2+}$  leaked from the ER. The fraction of IP3 receptors that is activated (h) is given by:

$$\frac{dh}{dt} = \frac{h_{\infty} - h}{\tau_h} \tag{13}$$

where  $h_{\infty}$  and  $\tau_h$  are given by:

$$h_{\infty} = \frac{Q_2}{Q_2 + Ca^{2+}} \tag{14}$$

$$\tau_h = \frac{1}{a_2(Q_2 + Ca^{2+})} \tag{15}$$

and

$$Q_2 = d_2 \frac{IP3 + d_1}{IP3 + d_3} \tag{16}$$

$J_{chan}$  is represented as follows:

$$J_{chan} = r_C m_\infty^3 n_\infty^3 h^3 (C_0 - (1 + C_1)Ca^{2+})$$

(17)

where,  $r_C$  is the maximum Calcium Induced Calcium Release (CICR) rate,  $C_1$  is the volume ratio of ER to cytoplasm and  $C_0$  is the amount of free calcium in the Cytoplasm,  $d_1$ ,  $d_2$  and  $d_3$  are constants. Moreover,  $m_\infty$  and  $n_\infty$  are given by:

$$m_{\infty} = \frac{IP3}{IP3 + d_1} \tag{18}$$

and

$$n_{\infty} = \frac{Ca^{2+}}{Ca^{2+} + d_{5}} \tag{19}$$

$m_{\infty}$  is the *IP3* Induced Calcium Release channel,  $d_5$  is a constant and  $n_{\infty}$  is the CICR channel.

Equations (20) and (21) quantify the leak channel as:

$$J_{legk} = r_L(C_0 - (1 + c_1)Ca^{2+})$$

(20)

and the pump channel as:

$$J_{Pump} = \frac{v_{ER} (Ca^{2+})^2}{k_{FR}^2 + (Ca^{2+})^2}$$

(21)

Where  $V_{ER}$  is the maximum rate of Calcium pumped into the ER,  $K_{ER}$  is a SERCA pump activation constant and  $r_L$  is the leakage rate of Calcium in the opposite direction.

Depolarization induced Suppression of Excitation (DSE) is assumed to have the following relation with AG:

$$DSE = AG * K_{AG}$$

(22)

The reason for including the scaling factor  $K_{AG}$  (=-4000) is to change the 2-AG level to a favourable negative range.

The internal calcium dynamics control glutamate release in this astrocyte model which is given as:

$$\frac{d(Glu)}{dt} = \frac{-Glu}{\tau_{Glu}} + r_{Glu} \,\delta(t - t_{Ca}) \tag{23}$$

$\tau_{Glu}$  and  $r_{Glu}$  are the (respective) decay and production rates of glutamate, and  $t_{Ca}$  is the time the calcium passes a certain threshold. Lastly, *eSP*, increase of synaptic transmission Probability of Release (PR), is given by:

$$\tau_{eSP} \frac{d(eSP)}{dt} = -eSP + m_{eSP} Glu(t)$$

(24)

Where  $\tau_{eSP}$  is the rate of eSP decay,  $m_{eSP}$  is a constant (fixed at 55\*10<sup>3</sup>).

The passive LIF neuron model [52] that is used in the self-repairing SANN can be given as:

$$\tau_m \frac{dv}{dt} = -v(t) + R_m \sum_{i=1}^n I_{syn}^i(t)$$

(25)

Where  $\tau_m$ , v and  $R_m$  are the membrane constant, potential and resistance, respectively,  $I_{syn}^i$  is the current injected to the neuron through synapse i.

A probabilistic based tripartite synapse model is used in this model where a random number between 0 and 1 is generated by a uniformly distributed pseudorandom number generator. The injected current is given by:

$$I_{syn}^{i}(t) = \begin{cases} linj & P_{rand} \leq PR_{(t)} \\ 0 & P_{rand} > PR_{(t)} \end{cases}$$

(26)

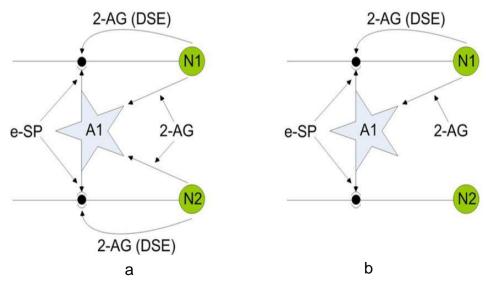

Where I<sub>inj</sub>=6650pA. In the case the network suffers no faults, as seen in Figure 2:3.a, the PR relating to each synapse is presented as:

$$PR_{(t)} = \frac{PR_{(t0)}}{100} * DSE_{(t)} + \frac{PR_{(t0)}}{100} * eSP_{(t)}$$

(27)

Here,  $PR_{(t0)}$  is the initial PR of each corresponding synapse. In this case each synapse activity is depressed by ~50% overall. When a major fault is present the equation can be rewritten as:

$$PR \to (\frac{PR_{(t0)}}{100} * eSP_{(t)})$$

(28)

With the absence of *DSE*, the PR sees an increase of 200% at the associated healthy synapse site. In short, it means that even if N2 is silent because of one or more faulty synapses, other healthy synapses or the recoverable faulty synapses still can bring N2 back to activity due to the indirect signalling from N1 via the astrocyte pathway.

This study implements the astrocyte model discussed in this section for several reasons. Firstly, as it is an in-house model the minute details of it is implementation is clear. These details are highly important when transferring such a complex model to hardware. Secondly, this model provides SNNs with self-repairing ability, making it extremely interesting for hardware implementation. It would be interesting to compare this model's hardware implementation with those of other astrocyte models in the literature in terms of power consumption and area footprint, however this falls beyond the scope of this work.

Figure 2:3 Interactions between the astrocyte and the two neurons between and after faults [6]

#### 2.2.3 Astrocyte Hardware Implementations

In this section, the efforts to realize astrocytes in hardware are reviewed.

Research has focused on hardware implementation of astro-neuron interactions using resource-efficient FPGA astrocyte hardware [53], [54]. The authors report that their model proves that firing rates of neurons can be modified by astrocytes and that astrocytes heavily regulate exchange of information at synaptic junctions. This is physically done my means of bi-directional channels between neurons and astrocytes. Single Constant Multiply (SCM) and linear approximation techniques have been used that permit deploying shift registers and adders instead of more resource-heavy components such as multipliers.

Linearization of the non-linear functions that represent biologically faithful astrocyte models has also been explored in the literature [55]. The linearization is done by using search algorithms for finding parameters that allow for lower cost hardware implementation while retaining reasonable accuracy. This technique has enabled the authors to implement an astrocyte hardware model without using DSP multipliers. Another similar work uses piecewise-linear approximation to eliminate the need for using multipliers while realizing astrocytes in FPGA hardware [56].

In other works [57], [58], an astrocyte model is put forward that breaks the synchronisation of two "Hopf" oscillators. The circuit is realized on FPGAs and the authors report a successful asynchronous operation of the "Hopf" oscillators.

Astrocytes have been incorporated into Intel's Loihi [59] many core neuromorphic processor [60] through connecting Loihi compartments and tuning the compartments' internal dynamics to mimic astrocytes behaviour. Loihi's original Software Development Kit (SDK) has been modified to allow for astrocyte implementation in the neuromorphic chip. The proposed Loihi Astrocyte Module (LAM) is able to reproduce the fundamental astro-neuron communication channels at the tripartite junctions as well as astrocytic intracellular calcium changes in response to synaptic activities. The three cases in which the effect of the proposed LAM is demonstrated are 1) How astrocytes modulate neuronal activity through their calcium dynamics; 2) How STDP mediated by astrocytes introduce single-shot pattern memorization; 3) How the transition between order and chaos can be sensed by astrocytes.

In addition to the digital implementations discussed so far, analogue realization of astrocytes has also been explored [8], [61],[62], [63]. Generally, analogue circuits are more compact and energy efficient than digital implementation. However, analogue circuits are more prone to noise and require more memory. Moreover, the existing Electronics Design Automation (EDA) tools cannot infer analogue circuit from HDL codes.

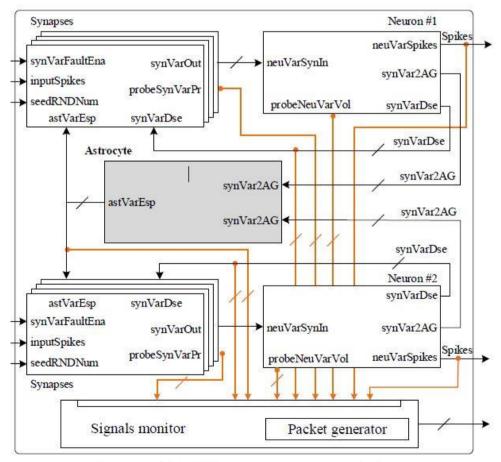

SPANNER (a hardware architecture, not to be confused with SPANNER project) is a hardware implementation of the astrocyte model (Section 2.2.1) that is used to perform self-repair in astrocyte-Neural networks [12]. In this work, an astrocyte monitors synaptic activities that happen in two adjacent neurons as shown in Figure 2:4. Encouraging results have been reported that demonstrates the ability of the astrocyte to recover the firing rate when faulty occurs on synapses. If the postsynaptic terminal is damaged beyond repair, the astrocyte will try to make up for the lost neural activity by increasing the rate at which the remaining healthy synapses belonging to the same neuron can fire.

The SPANNER architecture has been used to implement a simple controller for a robotic car [64] to demonstrate the principle.

A modified SANN has also been developed in hardware that uses STDP and BCM rules to facilitate learning and self-repair [65]. The astrocyte in this model regulates spike transmission between the two layers of the network, effectively acting as a frequency filter. Whenever a fault occurs (manifested by lowering of a target neuron's firing rate) the learning window will be re-opened, and the target neuron's frequency reaches its previous value again after the end of training window. The proposed SANN has been made the bases of a controller that allows a robotic car to avoid obstacles and follow a particular colour. This work has been realized using time domain multiplexing for reducing interneuron hardware overhead in a different publication [66].

Optimizing resource consumption of a hardware implementation of the astrocyte model [6] has been explored in SPANNER project [67]. Some of the biologically detailed features of the astrocyte process have been removed. The result is a resource-optimized astrocyte model that is less faithful in terms of biological dynamics but can still perform self-repair in SANNs. Further optimizations have been carried out through modifying equation parameters that allow for simpler and less resource-hungry implementation.

Finally, research undertaken as part of SPANNER project has focussed on using homeostatic principle in neurons for self-repair [68], [69]. No astrocyte is implemented in this work as, instead, homeostatic has been achieved by; 1) Designing neurons with variable firing voltage threshold; and 2) Using FPGAs' Partial Dynamics Feature for adjusting the operating frequency of the neurons.

#### • The limitations of the available approaches

Apart from SPANNER [67], [70], none of the other approaches aimed at providing SNNs with fine-grained self-repairing ability. Several of the astrocyte hardware implementations do not report any applications [55], [56]. Other works apply astrocytes for regulating and improving neuronal activity [53], [54]. However, on top of inability to self-repair, no solid infrastructure has been provided in these works for scalability beyond one FPGA devices. Furthermore, the reported approaches lack re-configurability and ability of data acquisition, the features that are incorporated in the AstroByte platform. Other published applications of astrocytes are not related to SNNs [57], [58].

#### 2.2.4 Hardware Interconnection Paradigms for Astrocytic Signalling

The focus of this research is designing a multi-FPGA, scalable and programmable platform for SANN acceleration called AstroByte. Among its many attributes, AstroByte can send astrocytic data, namely eSP, to nearby neurons. This section will outline similar work that deal with the challenge of communicating astrocytic data through scalable structures.

The first interconnection architecture to be referred to is H-NoC [71]. In fact, H-NoC, in its original form, is designed for SNNs as opposed to SANN. However,

Figure 2:4 SPANNER hardware architecture [12]

since H-NoC will be improved on by several works that will be discussed in this section, it will be studied here.

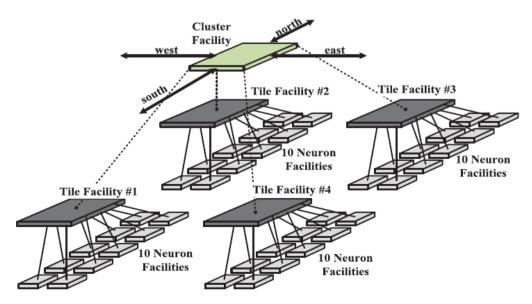

H-NoC is a hierarchical and scalable NoC architecture for large scale SNN implementation as can be seen in Figure 2:5. At the bottom of the hierarchy exist the neuron facilities, each composing of a node router and four neuron cells. Ten such neuron facilities are interconnected using a tile router which, as well its ability to route spikes between neuron facilities, can also route data to the next layer in the hierarchy. Cluster routers are placed at the top of the hierarchy to create cluster facilities which route SNN packets between four tile facilities and other cluster facilities. Another feature of H-NoC is its utilization of a compression technique that enhances throughput and decreases traffic overhead.

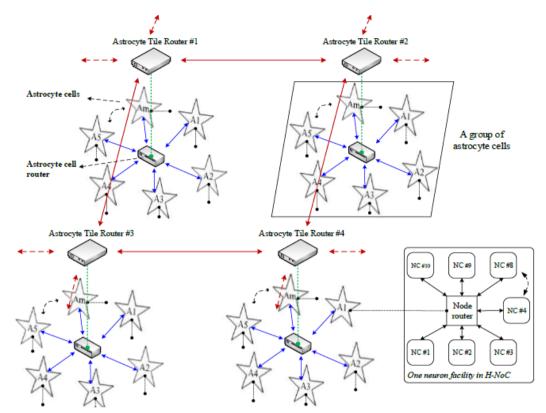

H-NoC has been modified to accommodate for astrocytic communications with neurons as well with each other, giving rise to HANA - Hierarchical Astrocyte Network Architecture [72], [73]. HANA main components are astrocyte cells and astrocyte tile facilities. Large scale astrocytic networks can be realized by using a number of astrocyte tile facilities as shown in Figure 2:6. A number of communication approaches have been applied which are broadcast in one tile, broadcast among a different tile's astrocyte cells, point-to-point with in one tile and point-to-point between astrocyte cells in different tiles. This will manage traffic both globally and locally and achieves traffic balancing.

Figure 2:5 H-NoC overall architecture [71]

Figure 2:6 HANA overall architecture [61]

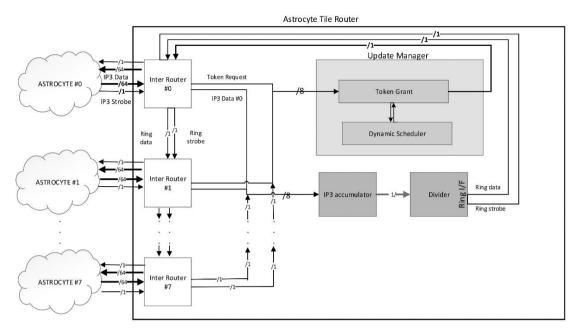

Further research has been carried out for establishing astro-neuron interconnections [74], [75]. The overall architecture is similar to the works mentioned above [72], [73] but differ in implementation details. Here, an astrocyte tile router has been used for regulating an IP3 pool among the astrocytes. Inter-routers have been implemented that serializes 64-bit IP3 values from the astrocyte for internal operations and parallelizes astrocyte-bound serial data that represents updated IP3 value. The overall architecture of the astrocyte tile router is shown Figure 2:7. The IP3 value from the astrocyte tile router is sent to all the astrocytes through an update manager that grants interneurons tokens for updating the IP3 pool value and then schedules updates to the astrocytic IP3 levels.

#### 2.3 SNN FPGA Implementations

Simulating SNNs has traditionally been performed using a programming language such as MATLAB or PyNN [76] that run on single or multicore general-purpose processors [77]–[80]. In addition, some researchers have focussed on implementing SNN simulations on GPUs [81]–[86].

FPGAs are another attractive option for simulating SNNs due to their on-field re-configurability and ability to realize dedicated hardware in a parallel manner [10], [87]. This has made FPGAs an interesting alternative to general purpose CPUs and GPUs for SNN realizations, whether it is for purely simulation, acceleration or application purposes.

Figure 2:7 Astrocyte tile router [75]

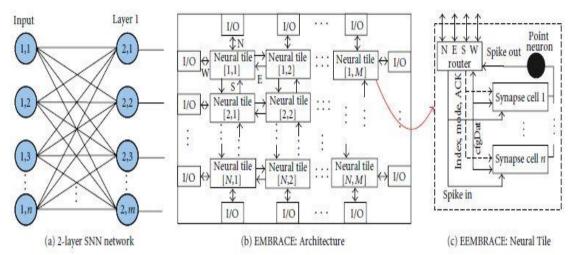

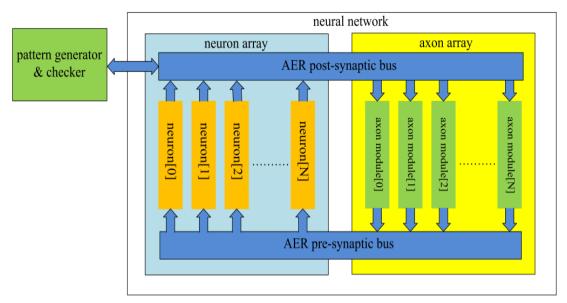

To this effect, the EMBRACE architecture, an in-house custom SNN structure that leverages NoC paradigm for scalable SNN FPGA simulations using a power and area efficient neuron model has been developed [10]. Embrace deploys a 2D mesh NoC structure that has a programmable neural tile router as its building block. The neural tiles can be reconfigured via packets that updates an address table to store the addresses of target presynaptic connections, defines the synaptic weights, and choses the model implemented for synaptic connections. An XOR problem was successfully mapped into an SNN created on EMBRACE architecture to verify its functionality. An overall architecture of Embrace platform is shown in Figure 2:8.

Subsequent work has realized an EMBRACE-based SNN that facilitates 32 neurons with 32 synapses each on Xilinx Virtex II-Pro FPGA device [88]. The XOR problem has been solved on the SNN, which has been incorporated into

Evo Platform – a Genetic Algorithm (GA) platform that aids in evaluating SNN features for various applications. Further research has been carried out to reroute traffic in the mesh interconnect in case of congestion, thanks to incorporating a router that is able to adapt to traffic patterns, avoiding dropped router packets when congestion happens [89]. A 4 x 2 EMBRACE architecture model was tested on an Intel Stratix II FPGA to demonstrate the new trafficadaptability feature.

A different approach has been adopted in NeuroFlow [87], a scalable platform for SNN simulation using FPGAs. This is a specialized processor with flexible architecture that can be modified to suit different configurations. It uses PyNN, an open source, neural network simulation language that is based on Python for modifying the processor architecture. Necessary compilation tools ensure translating high-level specifications of networks to FPGA implementations. Different models for neurons (e.g. LIF and Izhikevich) can be chosen and using

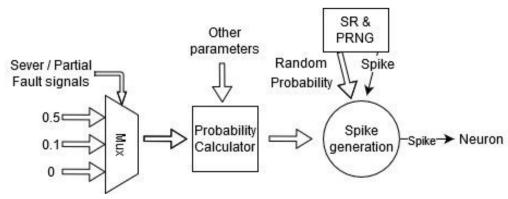

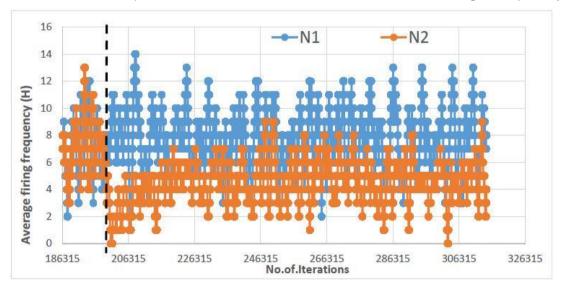

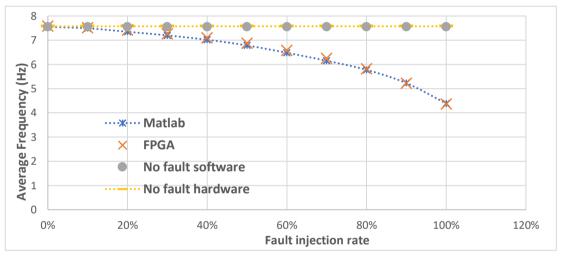

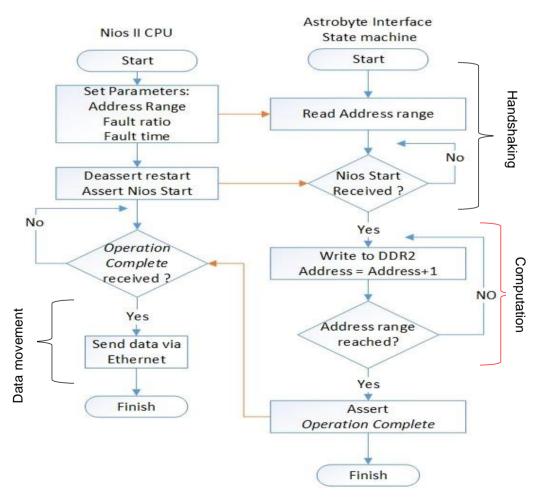

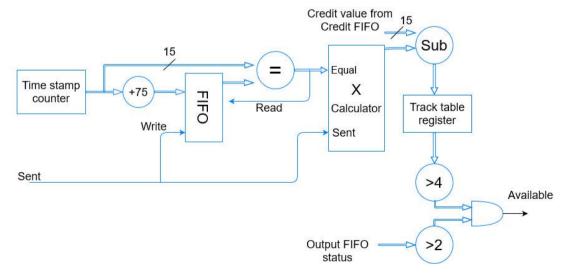

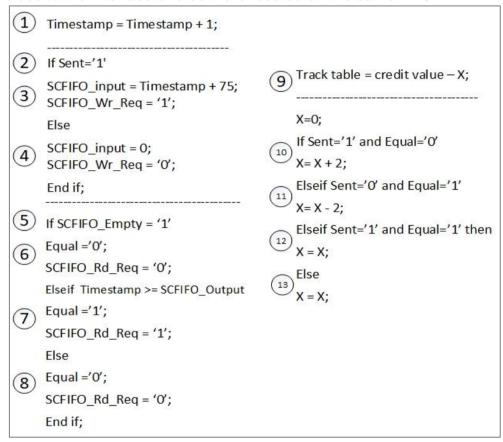

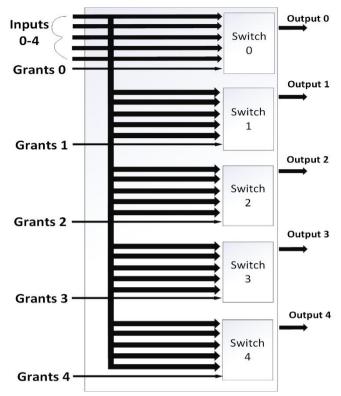

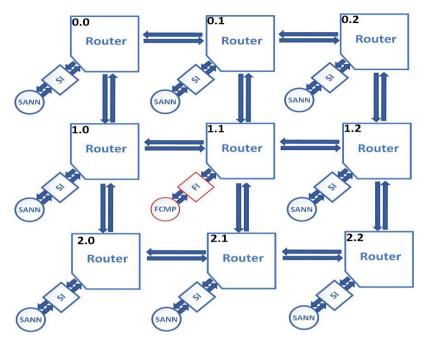

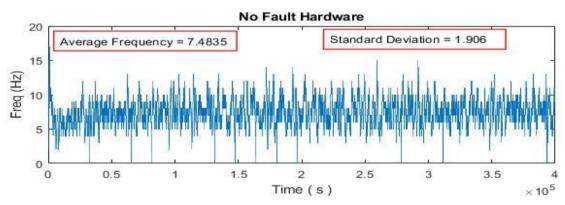

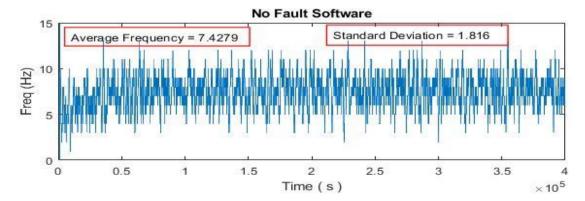

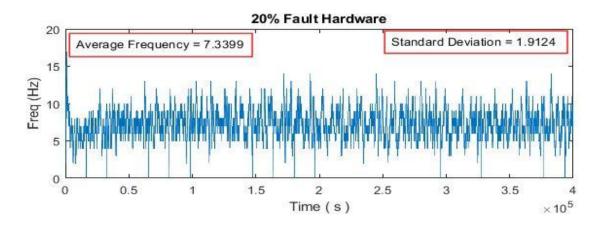

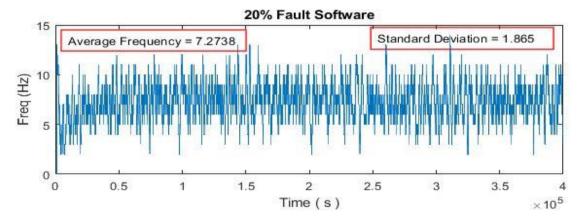

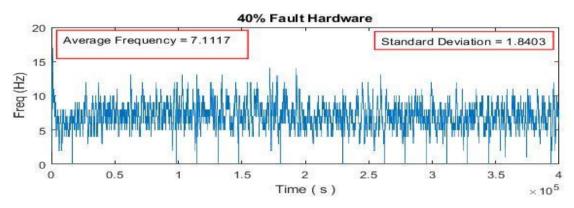

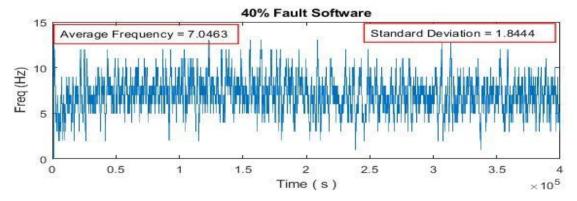

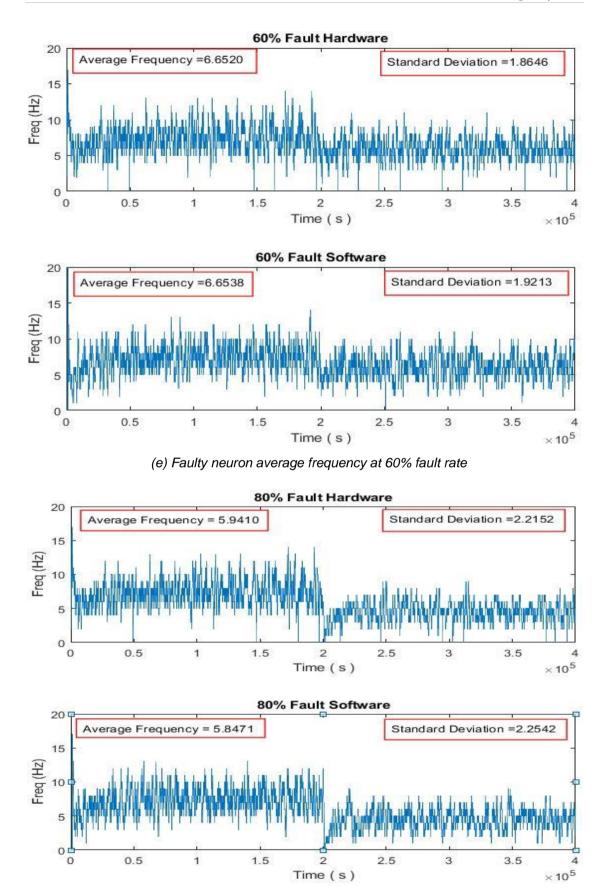

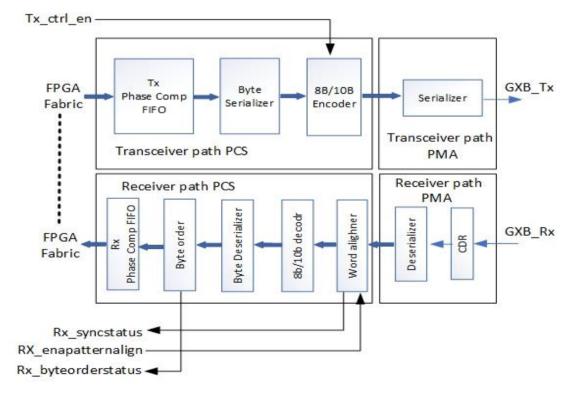

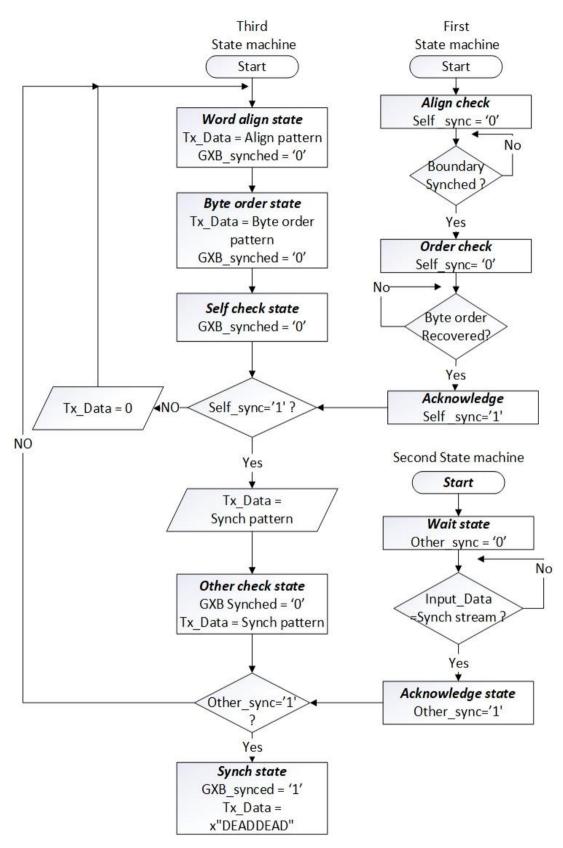

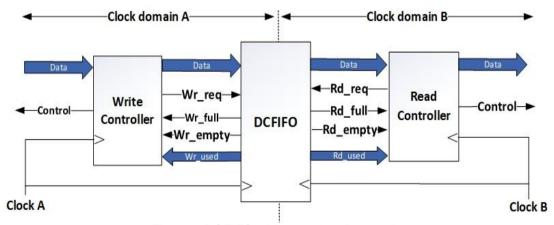

Figure 2:8 Embrace Architecture [10]